AMD新第二代3D V-Cache芯片细节-最高可达2.5 TB/s

AMD的Ryzen 9 7950X3D是世界上速度最快的game CPU,因为AMD决定将其颠覆性的3D芯片堆叠技术引入Zen 4。

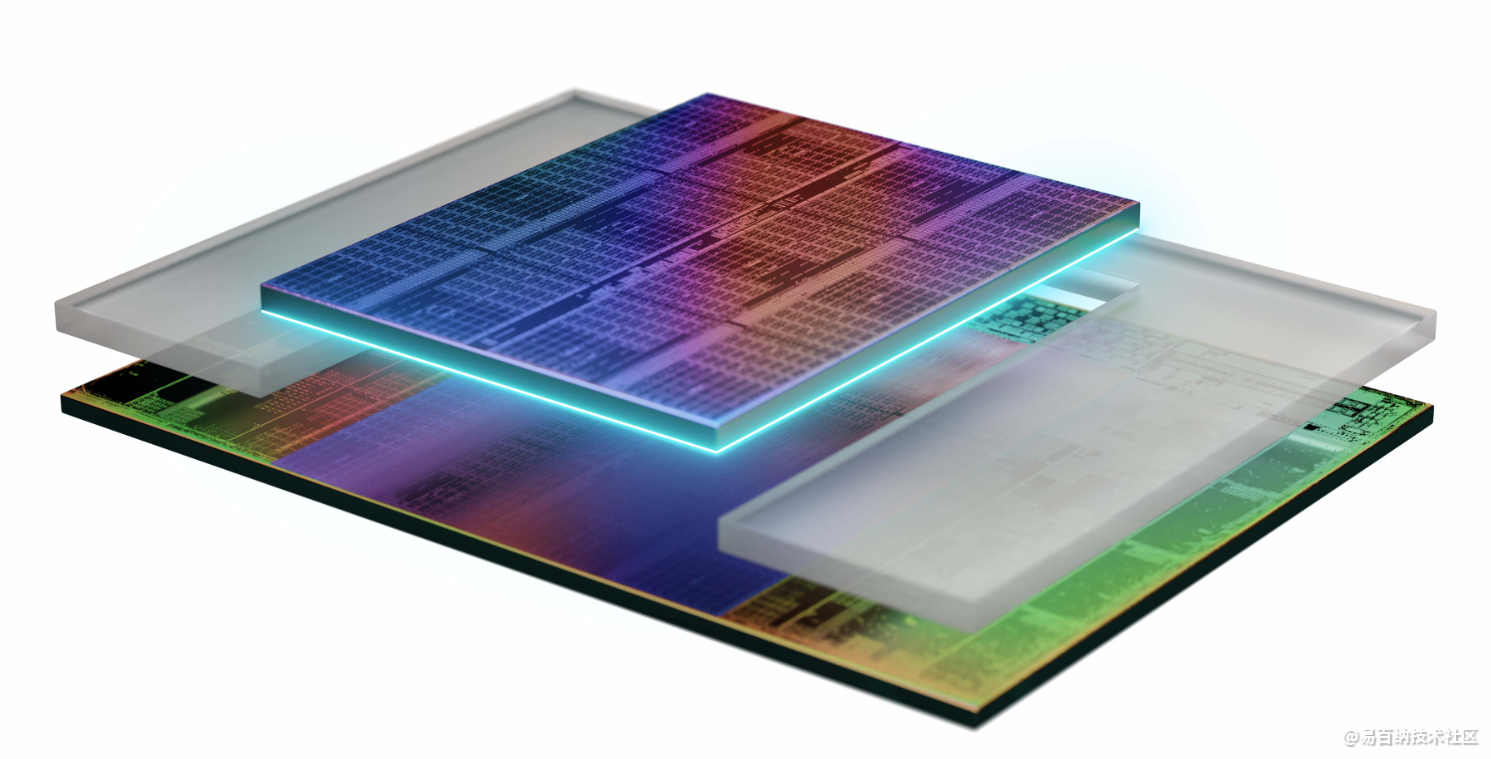

AMD已经推出了第二代3D V-Cache,而Intel没有竞争对手的技术。这确保了AMD在某些数据中心应用的最 佳CPU方面都取得了胜利。总的来说,AMD的第二代3D V-Cache技术比第一代技术进步了令人印象深刻的一步,因为它使公司能够利用现在成熟且成本较低的7nm工艺节点来提高其尖端5nm计算芯片的性能。新的设计代表了AMD利用基于小芯片的设计方法的关键优势——使用较旧且较便宜的工艺节点,结合昂贵的新工艺技术——进入第三维度。

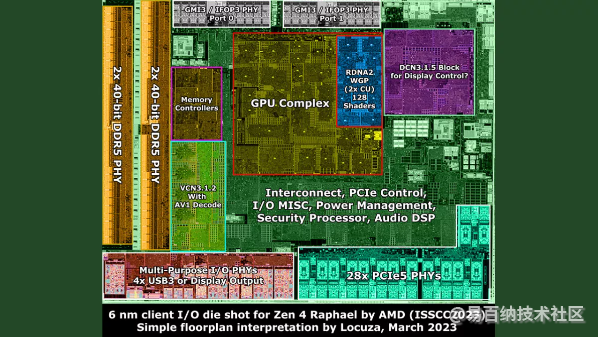

如上所述,AMD的3D V-Cache技术将一个额外的L3 SRAM小芯片直接堆叠在计算芯片(CCD)小芯片的中心,以将其与发热核心隔离。该缓存将配备3D V-cache的小芯片的容量提高到96MB,从而提高了延迟敏感应用程序的性能。

AMD的上一代3D V-Cache使用了堆叠在7nm Zen 3 CCD上的7nm L3 SRAM芯片。AMD坚持新L3 SRAM芯片(称为“L3D”)的7nm工艺,但现在将其堆叠在更小的5nm Zen 4 CCD上。然而,这造成了尺寸不匹配,需要进行一些修改。

| 第二代 2nm 7D V 型缓存芯片 | 第一代 7nm 3D V 型缓存芯片 | 5nm Zen 4 核复合芯片 (CCD) | 7nm Zen 3 核复合芯片 (CCD) | |

|---|---|---|---|---|

| 大小 | 36毫米^2 | 41毫米^2 | 66.3 毫米^2 | 80.7毫米^2 |

| 晶体管计数 | ~4亿 | 4亿 | 6亿 | 4亿 |

| MTr/mm^2 (晶体管密度) | ~130.6亿 | ~114.6亿 | ~99万 | ~51.4亿 |

首先,AMD将7nm SRAM芯片做得更小,所以它现在的尺寸是36mm2,而上一代的尺寸是41mm2。然而,晶体管的总数保持在47亿,因此新芯片的密度明显高于第一代芯片。

正如我们在第一代SRAM芯片上看到的,7nm L3 SRAM芯片具有令人难以置信的晶体管密度——我们看到的几乎是第一代7nm计算芯片密度的3倍,令人惊讶的是,7nm SRAM芯片的密度明显高于5nm计算芯片。这是因为,和以前一样,芯片使用了7nm的密度优化版本,专门用于SRAM。它也缺乏在缓存中发现的典型控制电路-电路驻留在基本芯片上,这也有助于减少延迟开销。相比之下,5nm芯片包括几种类型的晶体管以及数据路径和其他类型的结构,这些结构在简化的L3 SRAM芯片中不存在。

与之前一样,来自额外的L3 SRAM缓存的额外延迟为4个时钟,但L3芯片和基本芯片之间的带宽已经增加到2.5 TB/s,比之前的峰值2 TB/s提高了25%。

堆叠的L3 SRAM芯片通过两种类型的硅通孔(tsv -垂直电气连接)连接到基础模具。Power tsv在芯片之间传输功率,而Signal tsv在单元之间传输数据。

在第一代设计中,两种类型的tsv都位于基芯片的L3区域。然而,由于5nm工艺密度的增加,基础芯片上的L3缓存现在变小了,即使7nm的L3 SRAM芯片更小,它现在也重叠了L2缓存(前一代只重叠了基础芯片上的L3缓存)。因此,AMD不得不改变基本芯片和L3 SRAM芯片中的TSV连接。

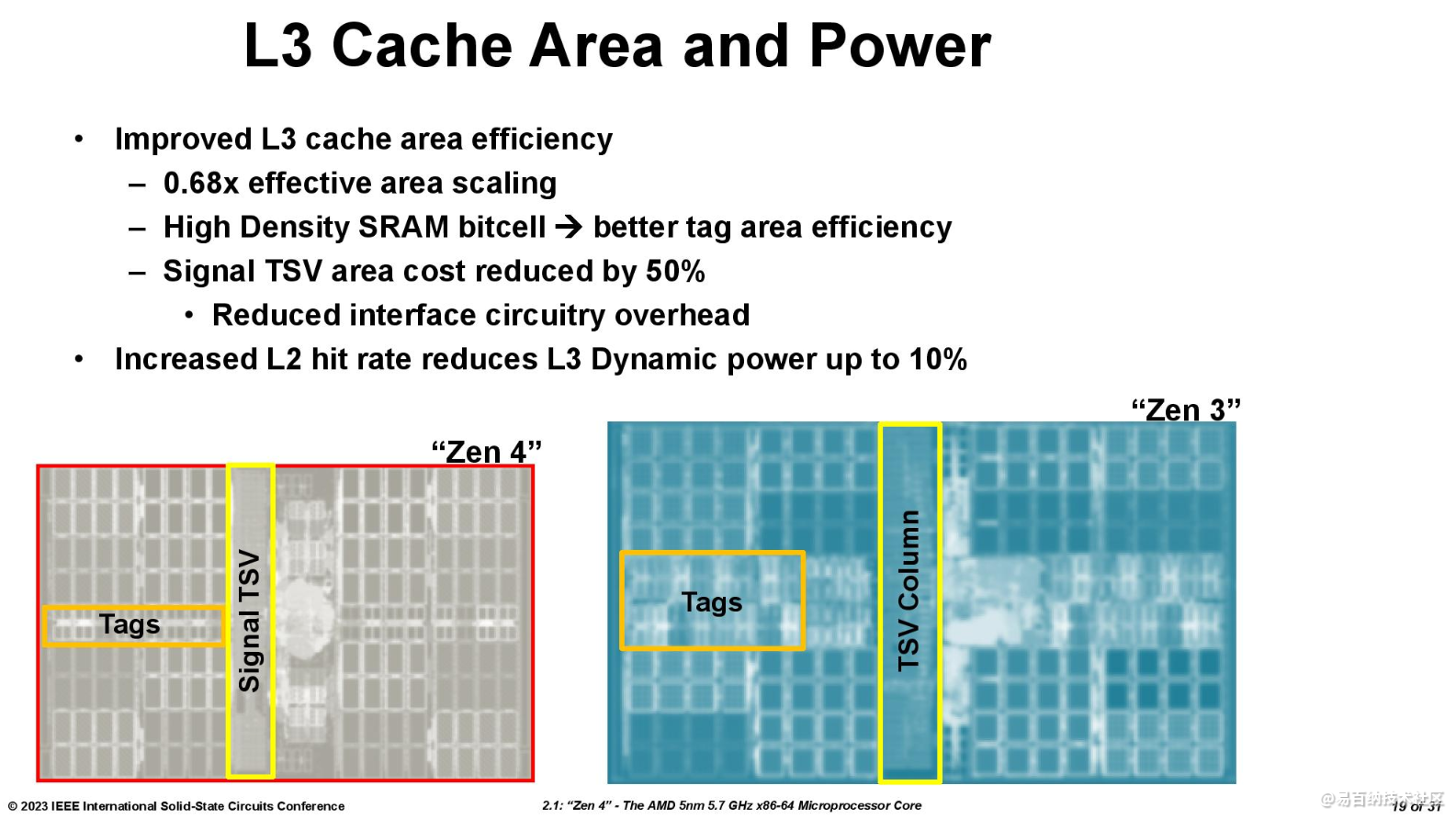

AMD不得不将功率tsv从L3扩展到L2区域,因为基本芯片上的5nm L3缓存尺寸较小(密度增加和其他因素造成的结果)。对于基础芯片,AMD在L3缓存、数据路径和控制逻辑上实现了0.68倍的有效面积缩放,与旧的7nm基础芯片相比,因此L3缓存中tsv的物理空间更小。

信号TSV保留在基本芯片上的L3缓存区域内,但AMD通过应用第一代设计的经验和DTCO改进来减少新接口设计中的开销电路,将L3缓存中的TSV区域缩小了50%。

AMD的3D芯片堆叠技术是基于台积电的SoIC技术。台积电的SoIC是无凸点的,这意味着它不使用微凸点或焊料来连接两个模具。AMD表示,它使用了相同的基本粘合工艺,并进行了持续的工艺和DTCO改进,但最小TSV间距没有改变。